he following

ssion of the copying for educational

"Customer (+44) 1865

wood Drive, ing Agency ax: (+44) 20

within their

ny article or

y form or by lisher.

oted above.

ucts liability, the material ug dosages

n does not afacturer.

the Author ok accepted guidelines,

en an article

no de Carlo, phone: (+1) /ier Science 5561 5047. gford Lane, sevier.co.uk

Journal of Systems Architecture 47 (2002) 759-761

## JOURNAL OF SYSTEMS ARCHITECTURE

www.elsevier.com/locate/sysarc

# Segmenting endoscopic images using adaptive progressive thresholding: a hardware perspective

K. Vijayan Asari <sup>a</sup>, T. Srikanthan <sup>b,\*</sup>

Department of Electrical and Computer Engineering, Old Dominion University, Norfolk, VA 23529, USA

Centre for High Performance Embedded Systems, School of Computer Engineering, Nanyang Technological University, Nanyang Avenue, Singapore 639798, Singapore

#### Abstract

Hardware realization of a novel technique based on adaptive progressive thresholding (APT) for the real-time segmentation of endoscopic images is presented. The APT algorithm is mapped onto a linear array of processing elements with each element of a particular segment communicating with its nearest neighbours. The efficiency and hardware portability of this technique justifies its use in applications that require high performance in real-time. © 2002 Elsevier Science B.V. All rights reserved.

Keywords: Endoscopic images; Adaptive progressive thresholding; Segmentation

## 1. Introduction

The lumen region and boundary in intestinal images form the preliminary basis of the features used for navigation and guidance in an automated endoscopy system. The high speed and accurate extraction of these features is essential for real-time robotic navigation. Since the endoscope uses several light sources at its tip and the illuminating distances of these sources are limited, the intestinal surface lying near the light source will be brighter than the farther ones. Hence, the areas of lowest intensity represent the lumen region in an image. Several researchers have presented various methods

to extract the lumen region from the endoscopic images [1,2]. An adaptive progressive thresholding (APT) technique for lumen extraction from a gray level endoscopic image is presented in this paper. Due to the excessive processing associated with image processing, many hardware implementation schemes for image processing have been presented in the literature [3,4]. A pipelined architecture for APT is proposed. The special purpose VLSI architecture uses an efficient encoding strategy to reduce the processing time as well as the communication time among the functional modules.

#### 2. Adaptive progressive thresholding

Otsu's thresholding is based on a discriminant analysis that partitions the image into two classes  $G_0$  and  $G_1$  at gray level 't' such that  $G_0 = \{0, 1, 1, 1\}$

E-mail address: astsrikan@ntu.edu.sg (T. Srikanthan).

1383-7621/02/\$ - see front matter © 2002 Elsevier Science B.V. All rights reserved. PII: S1383-7621(01)00027-3

<sup>\*</sup>Corresponding author. Tel.: +65-790-6965; fax: +65-792-0774.

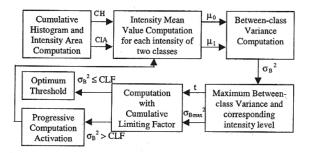

$2, \ldots, t$  and  $G_1 = \{t+1, t+2, \ldots, L-1\}$ , where L is the total number of gray levels in the image. The optimum threshold  $t^*$  can be obtained by maximising the between-class variance. Repeated application of Otsu's technique adaptively in a systematic fashion leads to a more accurate thresholded value and this procedure is named APT. Recursive thresholding is continued till the Cumulative Limiting Factor (CLF) defined as the ratio of between-class variance and total variance in every  $\Delta$ th iteration becomes less than a predefined value. That is, the iterative procedure is stopped and the final threshold value is obtained whenever

$$CLF(\Delta) < \alpha \frac{\mu_T}{\sigma_T^2},$$

(1)

where  $\alpha$  is a constant known as limiting parameter which can be trained using a number of images taken from a particular endoscopic camera. This takes into account the light intensity and distribution of the light sources mounted on the endoscope. The various computational steps involved in the APT algorithm are shown in Fig. 1.

#### 3. Pipelined architecture for APT

The hardware architecture consists of a pipeline of cells, each cell capable of performing a well-defined function. The input-output operations occur only at the boundary cells. The pipelined architecture for APT based on a linear array model with only nearest neighbour interconnections is developed for an 8-bit gray level image of

Fig. 1. Computational steps in APT.

size  $256 \times 256$ . Some variations in the computational steps of the APT algorithm have been adopted to satisfy the area-time efficiency requirements. The first stage in the architecture is associated with intensity histogram (IH) and intensity (IA) area computations. The 64 Kbytes image data is stored in four 16 Kbytes RAMs  $(R_1-R_4)$  and the data reading process is multiplexed. The second stage of the architecture is to compute IH and IA accumulation. In order to facilitate this, both the IH and IA registers in the first stage are circularly coupled so that the content of each register can be transferred to its nearest neighbour after every circular shift operation. The IH accumulation (IHA) and IA accumulation (IAA) are performed by successive addition and accumulating the sums in the ACC registers in each circular shift operation. The between-class variance  $\sigma_B^2$  is computed by successive multiplication. The  $\sigma_B^2$  values are then passed to a maximisation circuit to obtain  $\sigma_{B_{max}}^2|_i$ . Similarly 16 parallel blocks perform their computations simultaneously in a pipelined fashion for the computation of  $\sigma_{\rm B_{\rm max}}^2|_i$  for  $i=1,\ldots,16$ . The register arrays holding the contents of 16 different values of the  $\sigma_{\rm B_{max}}^2|_i$ for i = 1, 2, ..., 16 and the corresponding  $t^*$  are then circularly shifted to enable the computation of the maximum value  $\sigma_{B_{max}}^2$ . If the maximum value obtained is greater than  $\alpha \mu_T$ , the progressive threshold operation is activated and the threshold  $t_i^*$  obtained is used as the top value of the IHA and IAA. If the new  $\sigma_B^2$  satisfies the stipulated condition, the optimum threshold is obtained.

# 4. Results and discussion

The APT algorithm was tested using a large number of endoscopic images of size  $256 \times 256$ . 8-bit gray level images were generated from the original colour images and a filter of size  $3 \times 3$  was used to smoothen the images. The APT technique produced better results, as it is independent of the absolute gray level of the pixels contained in the darkest region. The optimum value of limiting parameter  $\alpha$  was chosen using a training-set of images and was found to be 8.3 in our application.

Fig. 2. Se nal image

A typica threshol respectiv posed I taken w envisage increase ogy wil time.

# 5. Concl

An a real-time doscopic chip mer of size 2 tual fab: Further reconfig tioning

computalave been ziency reitecture is () and in-54 Kbytes es RAMs is multicture is to order to ters in the he content its nearest ation. The umulation lition and egisters in ween-class nultiplicaa maximi-16 parallel Itaneously itation of ys holding the  $\sigma_{\rm B_{max}}^2|_i$ ing t\* are outation of num value rogressive threshold e IHA and ted condi-

ng a large  $256 \times 256$ . from the  $3 \times 3$  was technique sendent of national in of limiting ling-set of pplication.

Fig. 2. Segmentation of a typical endoscopic image. (a) Original image (b) Thresholded image.

A typical endoscopic image and the corresponding thresholded image are shown in Figs. 2(a) and (b), respectively. Performance evaluations of the proposed hardware confirm that the overall time taken was about 0.16 ms for the same image. It is envisaged that an improved pipeline design with increased parallelism in deep sub-micron technology will significantly shorten the computation time.

#### 5. Conclusion

An area-time efficient architecture for the real-time implementation of APT to segment endoscopic images has been proposed. Currently, on-chip memory core based VLSI design for an image of size  $256\times256$  is being implemented for eventual fabrication using 0.35  $\mu m$  CMOS technology. Further research work is in progress to develop a reconfigurable architecture by appropriate partitioning of various modules in the system.

#### References

- M. Cheriat, J.N. Said, C. Suen, A recursive thresholding technique for image segmentation, in: IEEE Transactions on Image Processing, 7, 1998, pp. 918–921.

- [2] N. Otsu, A threshold selection method from gray level histogram, in: IEEE Transactions on Systems Man and Cybernetics, 8, 1978, pp. 62-66.

- [3] N. Ranganathan, K.B. Doreswamy, A systolic algorithm and architecture for image thinning, in: Proc. IEEE GLSVLSI'95, 1995, pp. 138-143.

- [4] J.E. Eklund, C. Svensson, A. Astrom, VLSI implementation of a focal plane image processor – A realisation of the nearsensor image processing concept, in: IEEE Transactions on VLSI Systems, 4, 1996, pp. 322–335.

Vijayan K. Asari received his BSc. Engineering degree in Electronics and Communications from University of Kerala in 1978, and M.Tech. and Ph.D. degrees in Electrical Engineering from Indian Institute of Technology, Madras in 1984 and 1994, respectively. He is currently working as an Associate Professor in Electrical and Computer Engineering at Old Dominion University, Virginia, USA. His research interests include digital image processing, artificial neural netrols of the processing and the control of the processing and the processing artificial neural netrols of the processing artificial neural netrols and the processing artificial neural netrols of the processing and the processing artificial neural netrols of the processing and the processing artificial neural netrols of the processing and the processing artificial neural netrols of the processing artificial neural netrols of the processing and the processing artificial neural netrols of the processing and the processing artificial neural netrols of the processing artifical neural netrols of the processing artifical neural netrols of the processing artificial neural netrols of the processing art

image processing, artificial neural networks, and high performance digital architectures for application specific integrated circuits. He is a senior member of the IEEE

T. Srikanthan has been with Nanyang Technological University, Singapore since 1991 where he is an Associate Professor and Director of the Centre for High Performance Embedded Systems. He received his B.Sc. (Hons) in Computer and Control Systems and Ph.D. in System Modelling and Information Systems Engineering from Coventry University, United Kingdom. His research interests include system integration methodologies, architectural translations of compute

intensive algorithms, high speed techniques for image processing and dynamic routing. He is a corporate member of the IEE and a senior member of the IEEE.