# Chapter 4:

# Table of Contents

# Decoders

# Table of Contents

| Modular Combinational Logic - Decoders                            | 2  |

|-------------------------------------------------------------------|----|

| The generic decoder                                               | 2  |

| The 74139 decoder                                                 | 3  |

| The decoder specification sheet                                   | 4  |

| A decoder with active High outputs                                | 8  |

| A Negative Logic Solution                                         | 8  |

| The 3/8 decoder                                                   | 9  |

| The 4/16 decoder                                                  | 11 |

| Decoder Case Study #2: Implementing a Binary Adder with a Decoder | 16 |

## Modular Combinational Logic - Decoders

#### The Generic Decoder

A decoder is a min-term generator with each output corresponding to a single min-term. They are generally used for code conversions (binary to decimal), data routing, or equation creation. They are also referred to as "line decoders" due to the fact that the user can "activate" an output line by specifying a "control word".

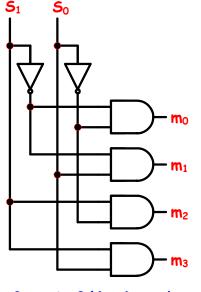

The *generic* discrete 2/4 decoder in the figure to the right has active high inputs and outputs. Each output (or minterm) in the circuit is produced by AND'ing the specified control signals  $S_1$ ,  $\overline{S_1}$ ,  $S_0$ , or  $\overline{S_0}$ , which results in a unique

output. It should be noted that there is absolutely NO way that

Generic 2/4 Decoder

<u>more than one output can be active at the same time.</u> The terminology 2/4 indicates that two inputs decode into four outputs.

As stated earlier, a **decoder** will **ALWAYS** have ONE and ONLY ONE **ACTIVE** output at a time. Normally, you will have two **2:4** Decoders on a single 14 pin chip. As is demonstrated in the circuit below, by combining the outputs with 'OR' gates you can create unique **SOP** equations.

It should be obvious to the student that the fewer the number of chips it takes to produce a logic expression:

- the lower real-estate on the printed circuit board,

- the lower power dissipation,

- the lower the manufacturing costs,

- fewer chips means higher reliability.

#### Generic Example:

In the example circuit to the right, a generic 2-4 decoder chip has one of its decoders being used to create two separate switching expressions.

Thus far, we have only discussed generic decoders with **active high** inputs/outputs. There are several popular decoders on the market which utilize **active high** and/or **active low inputs** and **outputs**. One such device is the **74139** as discussed next.

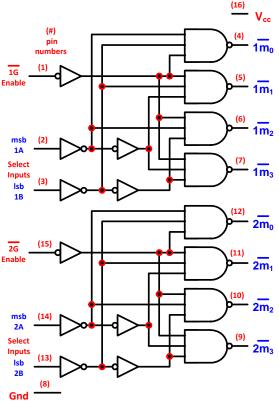

### The 74139 decoder

The **74139** is an excellent example of a **dual 2/4 decoder chip**. It features:

- Active High Inputs

- Active Low Outputs

- Active Low Enable Input

As can be seen in the circuit to the right, the enable, (G), goes to one input on each of the NAND gates. There is no way that anything except a high can be seen at the outputs unless this enable input is Active, (O). Therefore, if the device is disabled, all outputs go high since they are active low outputs. If they were active high outputs, they would go low when disabled.

Note the **additional inverter** in the select inputs shown in the diagram:

Question: What does it do?

Answer:

It improves the fan-in. To the Gnd outside world, it looks like one gate

vice three gates, which is what would be seen without the inverter.

#### The Decoder Specification sheet

Now let's examine a few entries on the 74139 specification sheet to the right.

|                              | S    |     |      |      |

|------------------------------|------|-----|------|------|

|                              | MIN  | NOM | MAX  | Unit |

| Supply Voltage               | 4.75 | 5   | 5.25 | V    |

| High-level input voltage     | 2    |     |      | V    |

| Low-level input voltage      |      |     | 0.8  | V    |

| High-level output<br>current |      |     | -0.4 | mA   |

| Low-level output current     |      |     | 8    | mA   |

- Note the difference between the maximum supply voltage and the recommended supply voltage.

- > This tends to be fairly standard with TTL devices.

- The table also indicates that a

- > "HIGH" is 2v or greater (High-Level Input Voltage)

- "LOW" is < .8v (Low-Level Input Voltage)</p>

- The high and low output currents are also given. However, as long as you don't exceed the fan-out, you don't have to worry about these items. There is one other item which is very important.

- > The Short Circuit Output Current No more than one output should be shorted or you could exceed this number.

- Again, this should not come as a surprise that if you SHORT outputs together that they will at the very least be degraded.

## 2/4 Decoder Examples

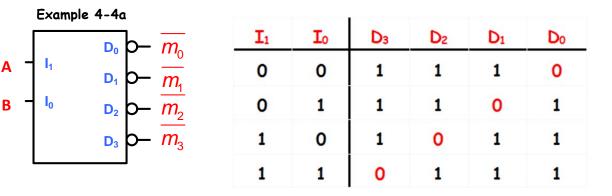

## Example 4-4a

Let's take a look at a decoder with <u>active low outputs</u>:

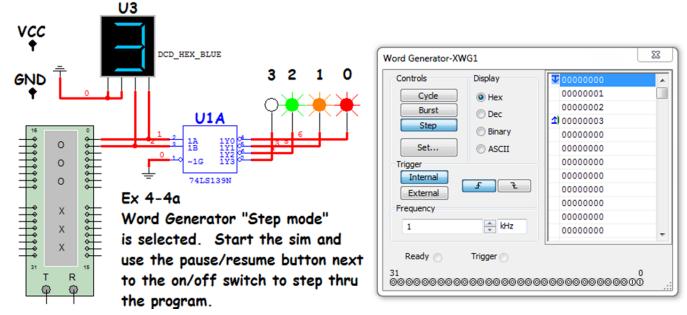

## Multisim Implementation of Example 4-4a

|                                                                                                          | 4 Lesson Notes (A)    Decoders    R.L. J                                                                                                                                                                                                                                                                                                           | ones                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10/26/2011                                                                                               |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                 | 6 OF                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Example 4-4b<br>$f(A, B) = \overline{\overline{m_1}}^*$<br>$= \overline{\overline{m_1}} +$<br>$= \sum m$ | $\frac{\overline{m_2}}{m_2} (NAND) = m1 + m2 = B = \frac{I_1}{I_0}$                                                                                                                                                                                                                                                                                | $\begin{array}{c} D_{0} & \bigcirc - & \overline{m_{0}} \\ D_{1} & \bigcirc - & \overline{m_{1}} \\ D_{2} & \bigcirc - & \overline{m_{2}} \\ D_{3} & \bigcirc - & \overline{m_{3}} \end{array} \xrightarrow{f}$ | (A,B)=∑m(1,2)<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                          | MultiSim implementation                                                                                                                                                                                                                                                                                                                            | m of 1 1b                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| tied to Bit - 2 o                                                                                        | rator is programmed as before. Note that<br>of the Word Generator which is always<br>he input to ground.                                                                                                                                                                                                                                           | it this time the Chip E                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| tied to Bit - 2 a<br>same as tying t<br>vcc<br>t =                                                       | rator is programmed as before. Note the                                                                                                                                                                                                                                                                                                            | it this time the Chip E                                                                                                                                                                                         | hus, it acts the                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| tied to Bit - 2 a<br>same as tying t<br>vcc<br>t =<br>GND<br>t                                           | rator is programmed as before. Note the<br>of the Word Generator which is always<br>he input to ground.                                                                                                                                                                                                                                            | Word Generator-XWG1                                                                                                                                                                                             | hus, it acts the                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| tied to Bit - 2 a<br>same as tying t<br>vcc<br>t =                                                       | rator is programmed as before. Note the<br>of the Word Generator which is always<br>he input to ground.                                                                                                                                                                                                                                            | Word Generator-XWG1                                                                                                                                                                                             | Was, it acts the   Wasser   Wasser |

| tied to Bit - 2 a<br>same as tying t                                                                     | pator is programmed as before. Note that<br>of the Word Generator which is always<br>the input to ground.                                                                                                                                                                                                                                          | Word Generator-XWG1                                                                                                                                                                                             | Was, it acts the   Wasser   0000000   0000001   0000001                                                                                                                                                                                                                                                                                                                                                                                                          |

| tied to Bit - 2 a<br>same as tying t                                                                     | DCD_HEX_DIG_GREEN                                                                                                                                                                                                                                                                                                                                  | Word Generator-XWG1<br>Controls<br>Cycle<br>Burst<br>Step<br>Step<br>Binary<br>Set<br>ASCII<br>Trigger                                                                                                          | bus, it acts the                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| tied to Bit - 2 a<br>same as tying t                                                                     | pator is programmed as before. Note that<br>of the Word Generator which is always<br>the input to ground.<br>DCD_HEX_DIG_GREEN<br>U2A<br>                                                                                                                                                                                                          | Word Generator-XWG1<br>Controls<br>Cycle<br>Burst<br>Cycle<br>Burst<br>Dec<br>Binary<br>Set<br>ASCII<br>Trigger<br>Internal                                                                                     | bus, it acts the                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| tied to Bit - 2 a<br>same as tying t                                                                     | pator is programmed as before. Note that<br>of the Word Generator which is always<br>he input to ground.<br>DCD_HEX_DIG_GREEN<br>U2A<br>                                                                                                                                                                                                           | Word Generator-XWG1                                                                                                                                                                                             | hus, it acts the                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| tied to Bit - 2 a<br>same as tying t                                                                     | DCD_HEX_DIG_GREEN<br>U2A<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1                                                                                                                                                                                                                                                          | Word Generator-XWG1<br>Vord Generator-XWG1<br>Cyde<br>Burst<br>Display<br>Hex<br>Dec<br>Binary<br>Set<br>ASCII<br>Trigger<br>Internal<br>Frequency                                                              | hus, it acts the                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| tied to Bit - 2 a<br>same as tying t                                                                     | pator is programmed as before. Note that<br>of the Word Generator which is always<br>he input to ground.<br>DCD_HEX_DIG_GREEN<br>U2A<br>                                                                                                                                                                                                           | Word Generator-XWG1<br>Word Generator-XWG1<br>Controls<br>Display<br>Cycle<br>Burst<br>Dec<br>Binary<br>Set<br>ASCII<br>Trigger<br>Internal<br>Frequency                                                        | hus, it acts the                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| tied to Bit - 2 a<br>same as tying t                                                                     | CD_HEX_DIG_GREEN<br>U2A<br>1 LOCD_HEX_DIG_GREEN<br>U2A<br>1 LOCD_HEX_DIG_GREEN<br>U2A<br>74LS139N<br>Ex 4-4b<br>The Word Generator is set to "Step Mode". Start the<br>sim with the On/Off switch and step thru the programmed<br>inputs with the "Pause/Resume" button next to the On/off<br>switch. You should get a High for min-terms 1 and 2. | Word Generator-XWG1<br>Vord Generator-XWG1<br>Cyde<br>Burst<br>Display<br>Hex<br>Dec<br>Binary<br>Set<br>ASCII<br>Trigger<br>Internal<br>Frequency                                                              | hus, it acts the                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| tied to Bit - 2 a<br>same as tying t                                                                     | DCD_HEX_DIG_GREEN<br>U2A<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1                                                                                                                                                                                                                                                          | Word Generator-XWG1<br>Vord Generator-XWG1<br>Vord Generator-XWG1<br>Cycle<br>Burst<br>Display<br>Hex<br>Dec<br>Binary<br>Set<br>ASCII<br>Trigger<br>Internal<br>Frequency<br>1<br>KHz                          | bus, it acts the                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

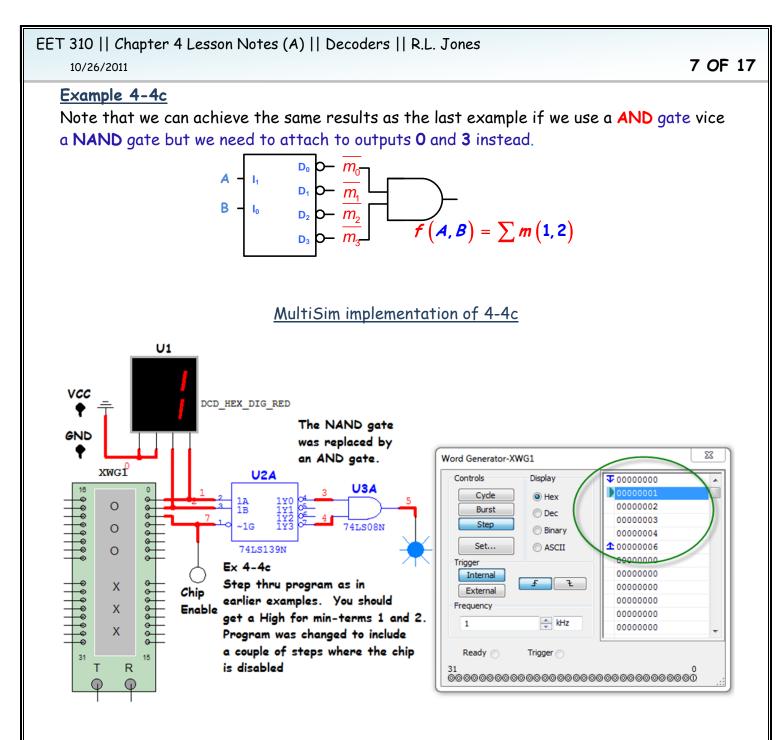

#### A decoder with active High outputs

Now let's look at a decoder with Active High Outputs compared with one with Active Low Outputs. The circuit above demonstrates that we can AND the ACTIVE LOW outputs that are not in our min-term list and get the desired min-term list. Note the difference in this circuit and the one on the previous page.

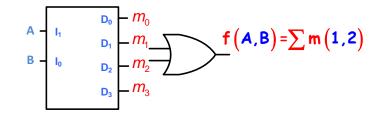

The circuit below has **ACTIVE HIGH** outputs. Note that we can use the more obvious **OR** gate for the solution.

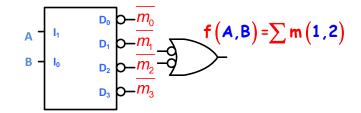

#### A Negative Logic Solution

**ACTIVE LOW** outputs sometimes give people trouble. Let's look at the same thing now but use **negative logic** to help clear up the situation.

Remember that an SOP expression is a SUMMATION of individual min-terms. Also remember that when we combine positive and negative logic, we can cancel out MATCHED Bubbles. So, if the matched bubbles are canceled we can see that we really do have:  $f(A, B) = \sum m(1, 2)$

Unfortunately, <u>MultiSim doesn't have Negative logic gates</u>. This is just a method of analyzing the circuit so that it means something.

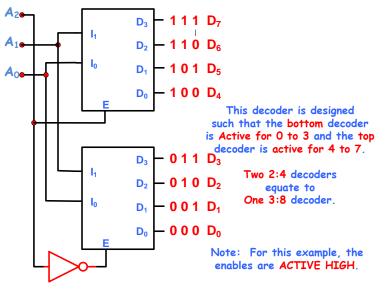

### The 3/8 decoder

Now, let's demonstrate how we can use two 2/4 decoders to build a single 3/8 decoder. This conversion is performed with the addition of an inverter to the circuit. As can be seen below, when one device is active, the other will be inactive. If we make the input to the Enable's the MSB of the input control word, we now have three inputs decoded to eight outputs.

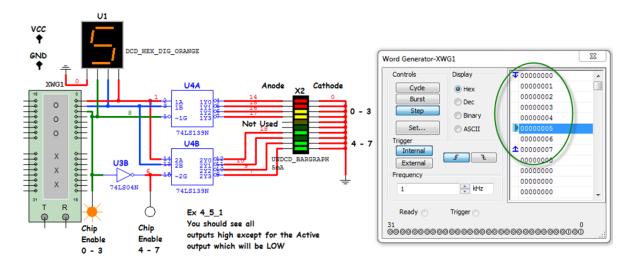

## MultiSim Example of building a 3/8 decoder

In this example the chip is enabled until the last 3 program steps.

| EET 310    Chapter 4 Lesson Notes (A)    Decoders    R.L. Jones |  |

|-----------------------------------------------------------------|--|

| 10/26/2011                                                      |  |

## The 4/16 decoder

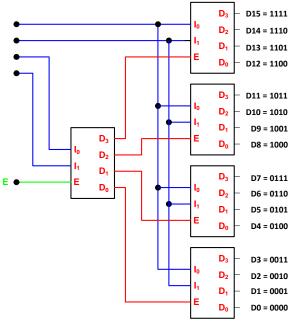

Let's take a look at an even larger decoder. We can create a 4/16 decoder using five 2/4 decoders.

In the figure, a fifth decoder is used to <u>select</u> which of the four other decoders is active.

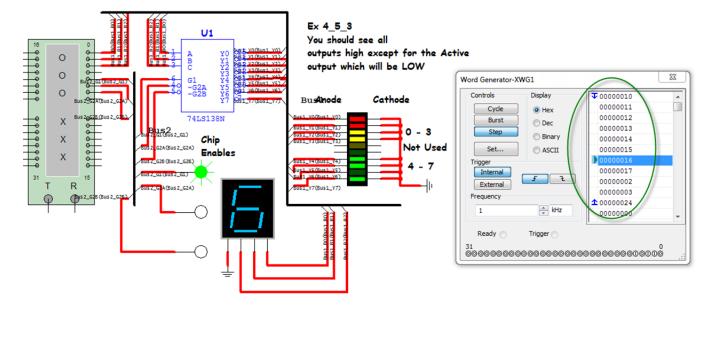

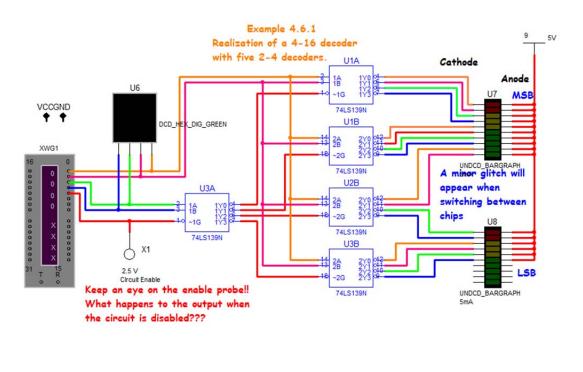

## A MultiSim Realization of a 5 chip 4/16 decoder

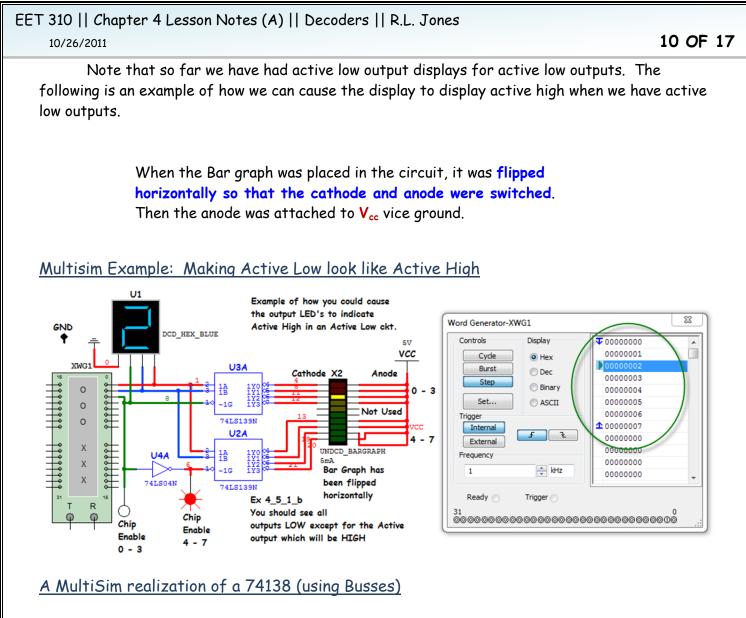

In the example below, remember that the outputs have been inverted to appear like they are active high by reversing the LED's at the output and tying them to  $V_{cc}$  vice ground.

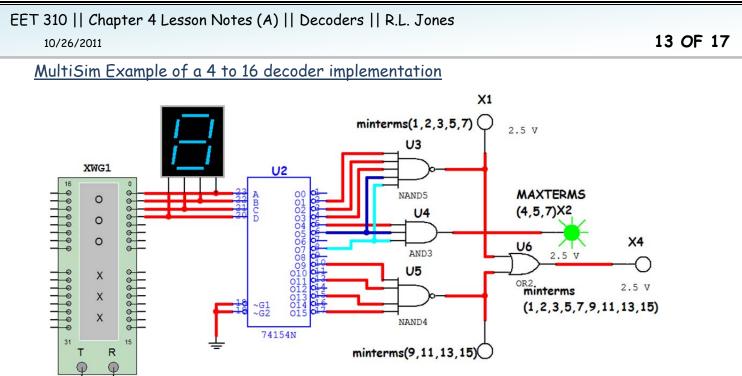

EET 310 || Chapter 4 Lesson Notes (A) || Decoders || R.L. Jones 12 OF 17 10/26/2011 The 74154 4/16 decoder The **74154** is an example of a popular "off-the-shelf" 4/16 decoder. 1 It features active high inputs and active low outputs, with two (msb) 2 active low enable inputs. Α 3 4 В Question: While the 74154 is a very popular decoder chip, 5 С 7 what are the advantages to using the five 2/4 6 7 decoders option instead? D 4 8 (lsb) 1 9 The 4/16 Decoder chip is a 24 pin dip with a 0.6" Answer: 5 10 center vice the 0.3" center for the 2/4 decoder 16 11 pin dip. If the 4/16 decoder chip was the only 24 12 pin chip on the PC board, the price of the 13  $G_1$ completed board might be cheaper if the designer 14 chose to use the 0.3" center devices instead. 15  $G_2$

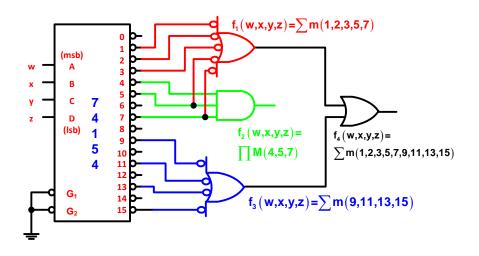

Let's look at the same example, but this time we used mixed logic to see if it makes the resulting expressions any clearer.

Remember that in mixed logic, if you can match bubbles, the bubbles cancel out.

Example 4-7-1

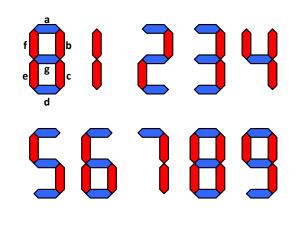

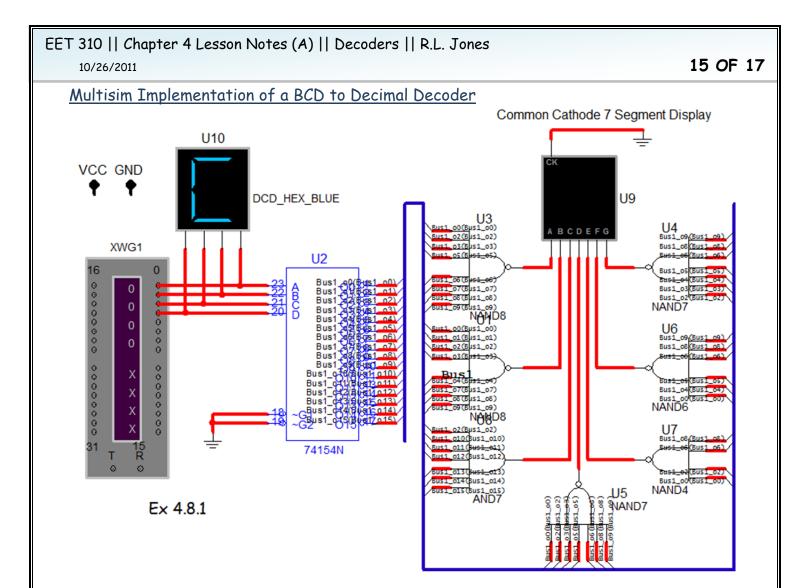

Decoder Case Study #1: BCD to Decimal Decoder

Of course, we have already designed a BCD to Decimal Decoder out of gates with the use of Kmaps and 'Don't Cares' in a previous chapter. But we could use just a **74154 4:16 decoder** to do the same job. Since the BCD numbers are equivalent to decimal numbers from 0-9, all we have to do is use the **74154** and ignore the outputs 10-15. This may be more expensive than using the cheaper gates but it **might save money** in the long run due to:

- cheaper construction cost and

- lower real estate taken up on the PC board.

And don't forget that the output of the 74154 is **negative logic** so you would have to take that into account.

| BCD input |                                   |   |   |  |   | Se | ven<br>De | -Se | - | ent |   |

|-----------|-----------------------------------|---|---|--|---|----|-----------|-----|---|-----|---|

| D         | С                                 | В | Α |  | ۵ | Ь  | С         | d   | e | f   | g |

| 0         | 0                                 | 0 | 0 |  | 1 | 1  | 1         | 1   | 1 | 1   | 0 |

| 0         | 0                                 | 0 | 1 |  | 0 | 1  | 1         | 0   | 0 | 0   | 0 |

| 0         | 0                                 | 1 | 0 |  | 1 | 1  | 0         | 1   | 1 | 0   | 1 |

| 0         | 0                                 | 1 | 1 |  | 1 | 1  | 1         | 1   | 0 | 0   | 1 |

| 0         | 1                                 | 0 | 0 |  | 0 | 1  | 1         | 0   | 0 | 1   | 1 |

| 0         | 1                                 | 0 | 1 |  | 1 | 0  | 1         | 1   | 0 | 1   | 1 |

| 0         | 1                                 | 1 | 0 |  | 1 | 0  | 1         | 1   | 1 | 1   | 1 |

| 0         | 1                                 | 1 | 1 |  | 1 | 1  | 1         | 0   | 0 | 0   | 0 |

| 1         | 0                                 | 0 | 0 |  | 1 | 1  | 1         | 1   | 1 | 1   | 1 |

| 1         | 0                                 | 0 | 1 |  | 1 | 1  | 1         | 1   | 0 | 1   | 1 |

| ,         | All other 0 0 0 0 0 0 0 0 0 0 0 0 |   |   |  |   | 0  | 0         |     |   |     |   |

| Gate Type<br>and Size<br>if a 74154<br>is used | Switching List (Fan-in minimized)                                   | Switching List (Fan-in minimized)                 | Gate Type<br>and Size<br>if a 74154<br>is used |

|------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------|

| NAND8                                          | $F_{a}(D, C, B, A) = \sum m(0, 2, 3, 5, 6, 7, 8, 9)$                | $F_{d}(D, C, B, A) = \sum m(0, 2, 3, 5, 6, 8, 9)$ | NAND7                                          |

| NAND8                                          | $F_{b}(D, C, B, A) = \sum m(0 - 4, 7 - 9)$                          | $F_{e}(D, C, B, A) = \sum m(0, 2, 6, 8)$          | NAND4                                          |

| AND 7                                          | $F_{c}(D, C, B, A) = \sum m (0, 1, 3 - 9)$ $= \prod M (2, 10 - 15)$ | $F_{f}(D, C, B, A) = \sum m(0, 4 - 6, 8, 9)$      | NAND6                                          |

|                                                |                                                                     | $F_{g}(D, C, B, A) = \sum m (2 - 6, 8, 9)$        | NAND7                                          |

(Note that the 7-segment display is a "common cathode" or "CK" type. In order for it to work in Multisim it SOMETIMES has to have the CK input grounded thru a 75 ohm resistor.)

EET 310 || Chapter 4 Lesson Notes (A) || Decoders || R.L. Jones 16 OF 17 10/26/2011 Decoder Case Study #2: Implementing a Binary Adder with a Decoder Contemporary Approach The truth table for a full adder is as follows: S. **BC**<sub>i</sub> В **C**<sub>i</sub> С. Α Α  $S_o = \overline{A} \ \overline{B}C_i + \overline{A}B\overline{C_i} + A\overline{B} \ \overline{C_i} + ABC_i$  $= A \oplus B \oplus C_i$ **BC**<sub>i</sub> Δ  $C_{o} = AB + AC + BC$  $= AB + C_i(A\overline{B} + \overline{A}B)$  $= AB + C_i (A \oplus B)$ A В So Ci Co Half Adder Half Adder

### 17 OF 17

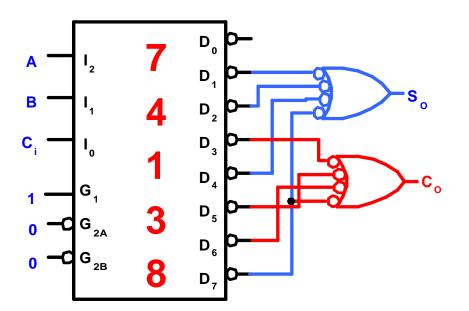

## Decoder Approach

From the Full Adder table on the previous page, we can derive the following min-term lists:

$$S_o(A, B, C_i) = \sum m(1, 2, 4, 7)$$

$C_o(A, B, C_i) = \sum m(3, 5, 6, 7)$

Note that we used the negative logic NAND gates to view this representation. We used a total of 2 chips to implement this circuit while the contemporary method used 3 chips (1 XOR, 1 AND, 1 OR).